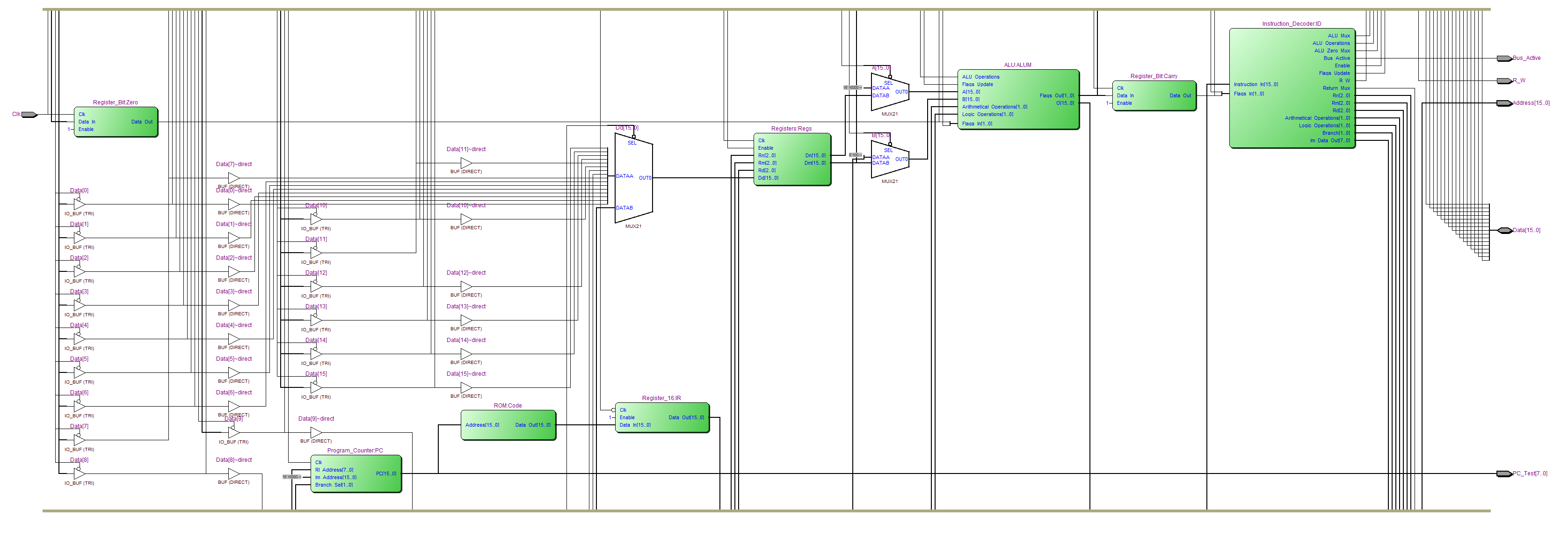

Önceki yazılarda tasarladığımız modülleri bu yazıda birleştirip, BT-I işlemcisine son halini vereceğiz. Modüllerin birleştirilmesi iç mimari yazısında gösterilen iç mimari şemasına göre yapılacaktır. VHDL kodu:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity BT_I is port(Clk : in std_logic; --Clk girişi Data : inout std_logic_vector(15 downto 0); --Çift yönlü veri ylu Address : out std_logic_vector(15 downto 0); --Adres yolu R_W, Bus_Active : out std_logic; --Yol kontrol çıkışları PC_Test : out std_logic_vector(7 downto 0)); --Debug için eklediğim 8 bitlik progam counter çıkışı end BT_I; architecture Behavioral of BT_I is --Önceden oluşturduğumuz komponentlerin çağrılması component Program_Counter port(Clk : in std_logic; Rl_Address : in std_logic_vector(7 downto 0); Im_Address : in std_logic_vector(15 downto 0); Branch_Sel : in std_logic_vector(1 downto 0); PC : out std_logic_vector(15 downto 0)); end component; component Registers port(Clk : in std_logic; Enable : in std_logic; Rn, Rm : in std_logic_vector(2 downto 0); Rd : in std_logic_vector(2 downto 0); Dn, Dm : out std_logic_vector(15 downto 0); Dd : in std_logic_vector(15 downto 0)); end component; component ALU port(A, B: in std_logic_vector(15 downto 0); Arithmetical_Operations : in std_logic_vector(1 downto 0); Logic_Operations : in std_logic_vector(1 downto 0); ALU_Operations : in std_logic; Flags_Update : in std_logic; Flags_In : in std_logic_vector(1 downto 0); Flags_Out : out std_logic_vector(1 downto 0); O : out std_logic_vector(15 downto 0)); end component; component Instruction_Decoder port(Instruction_In : in std_logic_vector(15 downto 0); Flags_In : in std_logic_vector(1 downto 0); Enable : out std_logic; Rn, Rm : out std_logic_vector(2 downto 0); Rd : out std_logic_vector(2 downto 0); ALU_Operations : out std_logic; Arithmetical_Operations : out std_logic_vector(1 downto 0); Logic_Operations : out std_logic_vector(1 downto 0); Flags_Update : out std_logic; Branch : out std_logic_vector(1 downto 0); ALU_Mux : out std_logic; ALU_Zero_Mux : out std_logic; Return_Mux : out std_logic; R_W : out std_logic; Bus_Active : out std_logic; Im_Data_Out : out std_logic_vector(7 downto 0)); end component; component Register_16 port(Clk : in std_logic; Enable : in std_logic; Data_In : in std_logic_vector(15 downto 0); Data_Out : out std_logic_vector(15 downto 0)); end component; --1 bitlik D tipi flip-flop component Register_Bit port(Clk : in std_logic; Enable : in std_logic; Data_In : in std_logic; Data_Out : out std_logic); end component; --Komut hafızası component ROM port(Address : in std_logic_vector(15 downto 0); Data_Out : out std_logic_vector(15 downto 0)); end component; signal Im_Data : std_logic_vector(7 downto 0); signal Branch : std_logic_vector(1 downto 0); signal PC_Out : std_logic_vector(15 downto 0); signal IR_Out : std_logic_vector(15 downto 0); signal ROM_Out : std_logic_vector(15 downto 0); signal Flags_In, Flags_Out : std_logic_vector(1 downto 0); signal Rn, Rm, Rd : std_logic_vector(2 downto 0); signal Dn, Dm, Dd : std_logic_vector(15 downto 0); signal Registers_Enable : std_logic; signal ALU_Operations : std_logic; signal Arithmetical_Operations, Logic_Operations : std_logic_vector(1 downto 0); signal Flags_Update : std_logic; signal ALU_Mux, ALU_Zero_Mux, Return_Mux : std_logic; signal R_WSignal : std_logic; signal A, B, O : std_logic_vector(15 downto 0); signal Bus_ActiveS : std_logic; begin --Program counterin yerleştirilmesi PC : Program_Counter port map(Clk, Im_Data, X"0000", Branch, PC_Out); --Program hafızasının yerleştirilmesi Code : ROM port map(PC_Out, ROM_Out); --Komut registeri(IR) IR : Register_16 port map(not Clk, '1', ROM_Out, IR_Out); --Komut çözücünün yerleştirilmesi ID : Instruction_Decoder port map(IR_Out, Flags_In, Registers_Enable, Rn, Rm, Rd, ALU_Operations, Arithmetical_Operations, Logic_Operations, Flags_Update, Branch, ALU_Mux, ALU_Zero_Mux, Return_Mux, R_WSignal, Bus_ActiveS, Im_Data); --Bayraklar Carry : Register_Bit port map(Clk, '1', Flags_Out(0), Flags_In(0)); Zero : Register_Bit port map(Clk, '1', Flags_Out(1), Flags_In(1)); --Genel kullanım registerlerinin yerleştirilmesi Regs : Registers port map(Clk, Registers_Enable, Rn, Rm, Rd, Dn, Dm, Dd); --İşlemci içi veri kontrol multiplexerları with ALU_Mux select B <= Dm when '0', (X"00" & Im_Data) when others; with ALU_Zero_Mux select A <= Dn when '0', X"0000" when others; with Return_Mux select Dd <= O when '0', Data when others; --ALU'nun yerleştirilmesi ALUM : ALU port map(A, B, Arithmetical_Operations, Logic_Operations, ALU_Operations, Flags_Update, Flags_In, Flags_Out, O); Address <= O; --Veri hattına R/W sinyali ile kontrol edilebilen tri-state buffer yerleştirilmesi with R_WSignal select Data <= Dm when '0', "ZZZZZZZZZZZZZZZZ" when others; R_W <= R_WSignal; Bus_Active <= Bus_ActiveS; --Program sayacının ilk 8 bitini debug için dışarıya aktardım PC_Test <= PC_Out(7 downto 0); end Behavioral;

Tasarımın Quartus II programı tarafından oluşturulan RTL şeması: