Bu yazı serimde FPGA (Field-Programmable Gate Array) üzerinden BT-I işlemcisinin tasarımını yapacağım. Serinin diğer yazılarına aşağıdaki linklerden ulaşabilirsiniz:

1.Giriş

2.İç Mimari

3.Dış Mimari

4.Program Counter

5.ALU Tasarımı

6.Register Tasarımı

7.Komut Seti Mimarisi ve Tasarımı

8.Instruction Decoder Tasarımı

9.İşlemcinin Tasarlanması

10.Uygulamalar

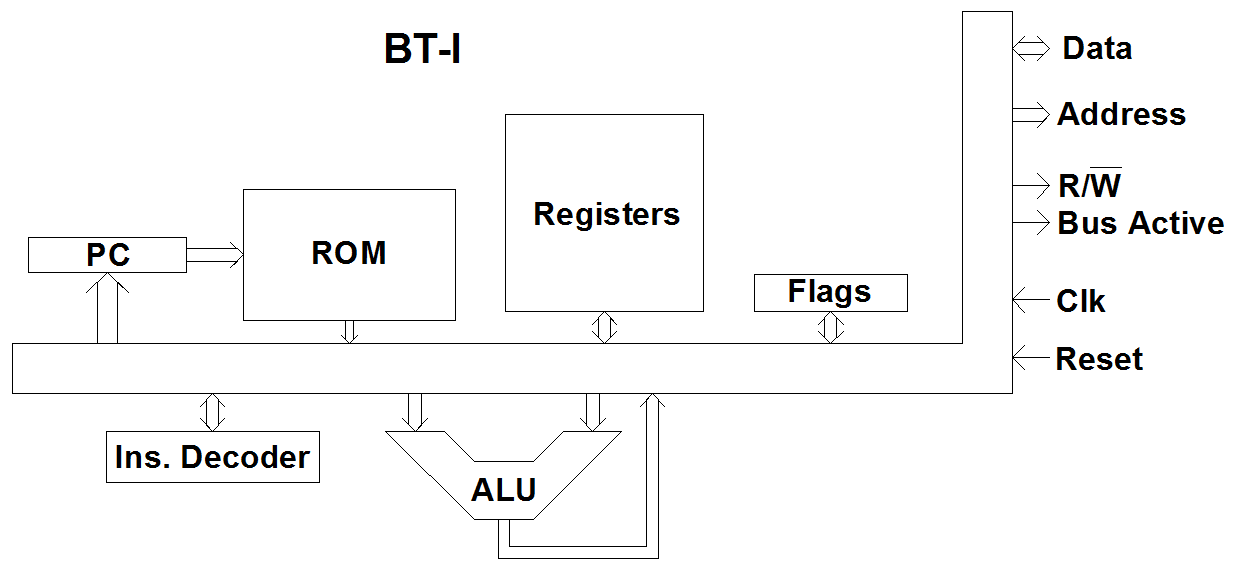

Tasarımı yaparken Intel'in x86 mimarisi ve ARM mimarisinden esinlendim. Tasarımı yapılacak işlemcinin özellikleri şu şekilde olacaktır:

İşlemci mimarisi:

- 16 - Bit

- RISC

Hafıza Mimarisi:

- Harvard

- Little Endian

Komut Seti Mimarisi:

- Tamamı 16 Bitlik SISD Tabanlı

Dış Mimari

- 16 - Bit Data Yolu

- 16 - Bit Adres Yolu (64Kb Adres Alanı)

Tasarımı olabildiğince basit tutmaya çalıştım. İşlemcinin 8 adet genel amaçlı 16 bitlik registeri bulunmaktadır. Bütün işlemler 1 cycle'da işlenmektedir. Program kodlarının depolandığı ROM'dan yalnızca komutlar alınabilir. Yani ROM'un içinden RO veriler okunamaz. ALU'da toplama, çıkarma, and, or ve not işlemleri yapılabilir. Çarpma ve bölme için alt programlar yazılabilir. Carry ve Zero olmak üzere 2 adet flag vardır. Bunlar B(Branch) komutu ile koşullu dallanma yapmak için kullanılabilir. Aşağıda mimarinin basit bir çizimi görülmektedir.