Bu yazı serimde BT-I işlemcisinin bir üst modeli olan BT-II işlemcisinin tasarımını ve FPGA üzerinde uygulamasını yapacağım.

Serinin diğer yazılarına aşağıdaki linklerden ulaşabilirsiniz:

1.Giriş

2.İç Mimari

3.Dış Mimari

4.Program Counter

5.Stack

6.ALU

7.Registers

8.ISA

9.Instruction Decoder

10.BT-II

11.Uygulamalar

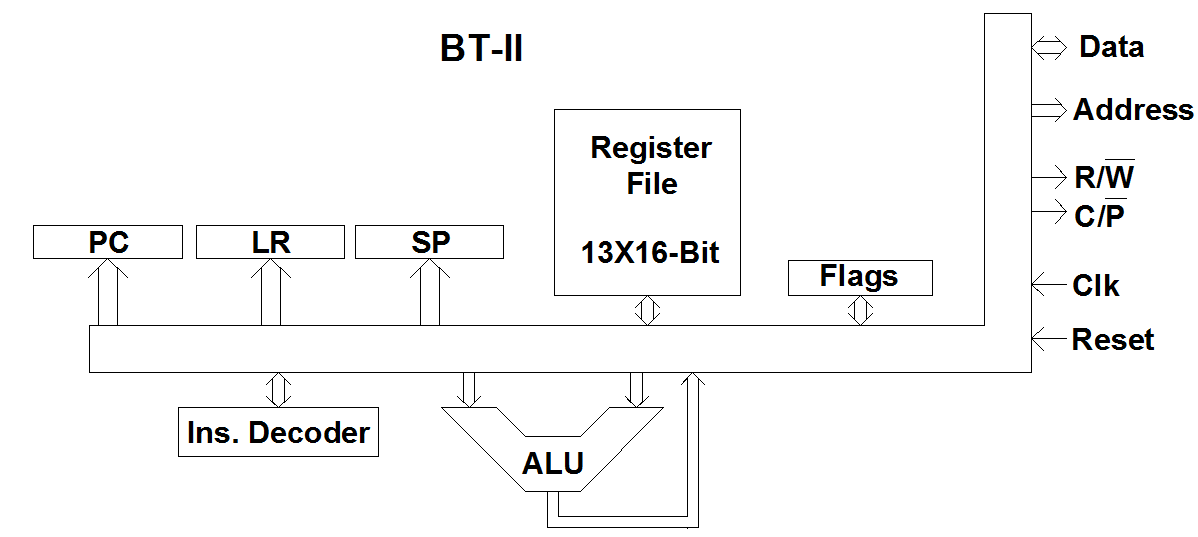

BT-II işlemcisinin özellikleri şu şekilde olacaktır:

İşlemci Mimarisi:

- 16 - Bit

- RISC

Hafıza Mimarisi:

- Von Neumann

- Little Endian

Komut seti mimarisi:

- 16 ve 32 Bitlik Tamamı SISD tabanlı

Dış Mimari:

- 16 - Bit Data yolu

- 16 - Bit Adres yolu (64Kb Adres Alanı)

BT-II'nin BT-I'den en önemli farkı 32 - Bitlik komutları da yürütebilmesidir. 32 - Bitlik komutlar sayesinde komut içinde daha büyük veriler taşınabilmektedir. BT-II işlemcisinin bir özelliği de Von Neumann mimarisinde tasarlanmış olmasıdır. BT-II'nin aritmetik ünitesi 16/8 bit toplama, 16/8 bit çıkarma işlemlerinin yanında 16x16 bit çapma işlemini de 1 cycleda yapabilmektedir. Ayrıca 16 bitlik barrel shifter sayesinde 1 cycle içinde shift işlemlerini yapabilmektedir. BT-II'nin BT-I'de olmayan bir diğer özelliği ise stack'e sahip olmasıdır. BT-II 16 tane registere sahiptir, bunlardan 13 tanesi genel amaçlı registerderdir. Geriye kalan 3 register program sayacı registeri, link registeri ve stack registeridir. Komutlar 2 ya da 3 cycleda gerçekleşir (M+E, M+M+E, M+M+(M,E)). BT-II'nin basitleştirilmiş tasarımı aşağıdadır: