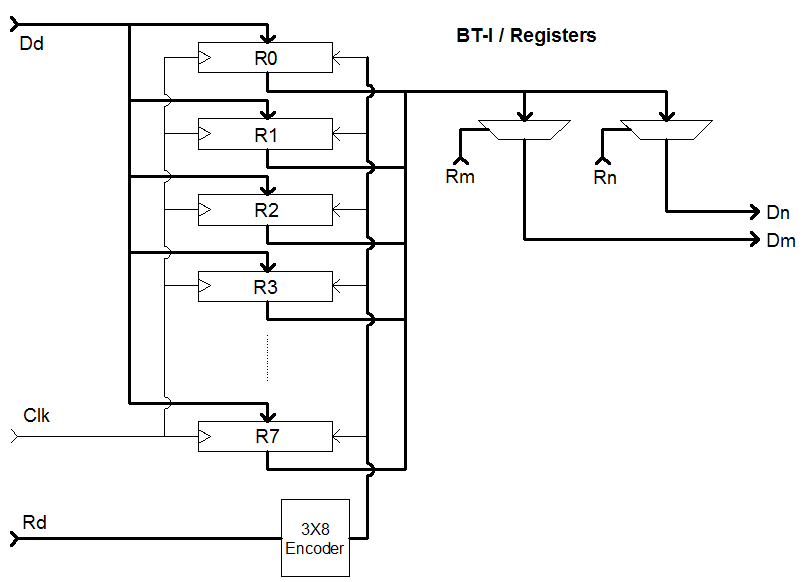

Registerler işlemcinin erişebileceği en hızlı hafıza birimidir. Statik yapıdadır. BT-I işlemcisinde 8 adet 16 bitlik genel kullanım registeri vardır. Her bir register Rn şeklinde isimlendirilmiştir. Registerlerin tasarımı şu şekildedir:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.std_logic_signed.all; USE ieee.numeric_std.ALL; entity Registers is port(Clk : in std_logic; --Clock girişi Enable : in std_logic; --Yazma aktif girişi Rn, Rm : in std_logic_vector(2 downto 0); --Rn, Rm seçimi Rd : in std_logic_vector(2 downto 0); --Rd seçimi Dn, Dm : out std_logic_vector(15 downto 0); --Rn ve Rm için data çıkışları Dd : in std_logic_vector(15 downto 0)); --Dd için data girişi end Registers; architecture Behavioral of Registers is --Komponent tanımlamaları component Register_16 port(Clk : in std_logic; Enable : in std_logic; Data_In : in std_logic_vector(15 downto 0); Data_Out : out std_logic_vector(15 downto 0)); end component; type signal_array is array (7 downto 0) of std_logic_vector(15 downto 0); signal Enable_Bits : std_logic_vector(7 downto 0); signal Register_Out : signal_array; begin --Registerlerin yaratılması U1 : for i in 0 to 7 generate U1 : Register_16 port map(Clk, Enable_Bits(i) and Enable, Dd, Register_Out(i)); end generate; --Multiplexerlar Dn <= Register_Out(to_integer(unsigned(Rn))); Dm <= Register_Out(to_integer(unsigned(Rm))); --3x8 Encoder with Rd select Enable_Bits <= "00000001" when "000", "00000010" when "001", "00000100" when "010", "00001000" when "011", "00010000" when "100", "00100000" when "101", "01000000" when "110", "10000000" when "111"; end Behavioral;

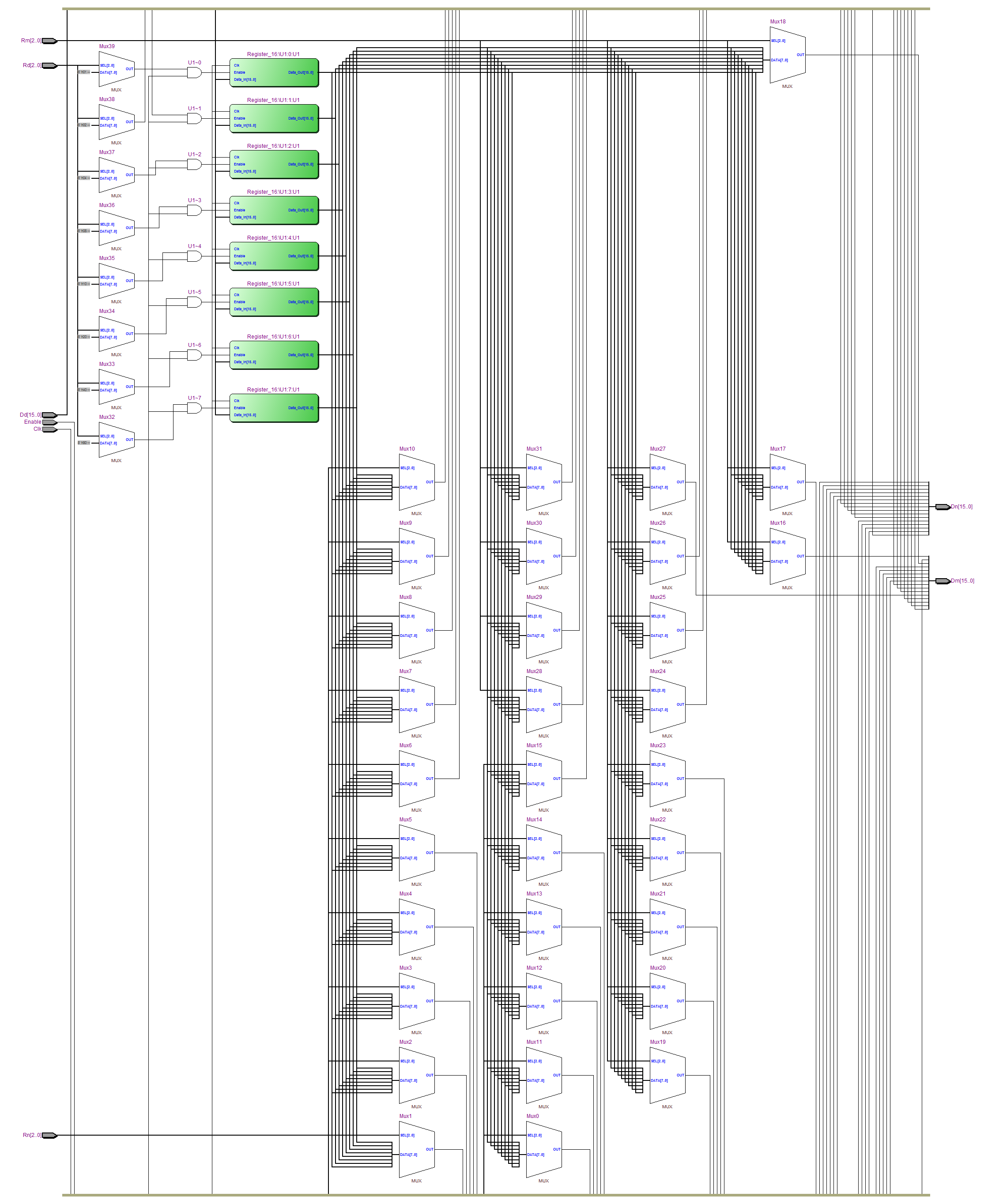

Tasarımın Quartus II programı tarafından oluşturulmuş RTL şeması: