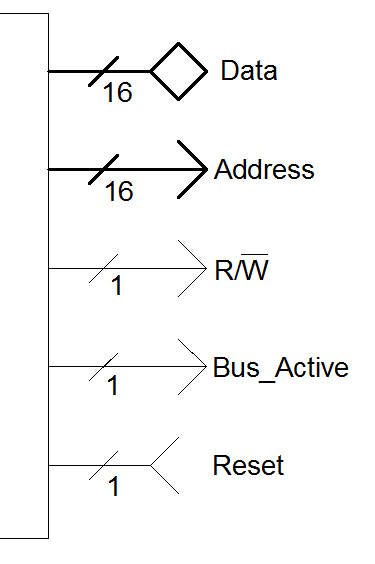

BT-I işlemcisinin dış mimarisi aşağıda görülmektedir.

Sinyaller

Sinyaller

Data: İşlemcinin dış dünya ile veri alışverişinin yapıldığı hat. 16 bit genişliğindedir ve çift yönlüdür.

Address: İşlemcinin hangi adres ile iletişim kuracağını belirten hat. 16 bit genişliğindedir ve işlemciye göre çıkış yönündedir.

R/W: '1' konumunda okuma, '0' konumunda yazma işlemenin yapılacağının belirtir. 1 bit genişliğinde, işlemciye göre çıkış yönündedir.

Bus_Active: '1' konumunda işlemcinin yazma ya da okuma işlemi yapacağını belirtir. 1 bit genişliğinde, işlemciye göre çıkış yönündedir.

Reset: '1' konumunda işlemci resetlenir. 1 bit genişliğinde, işlemciye göre giriş yönündedir.

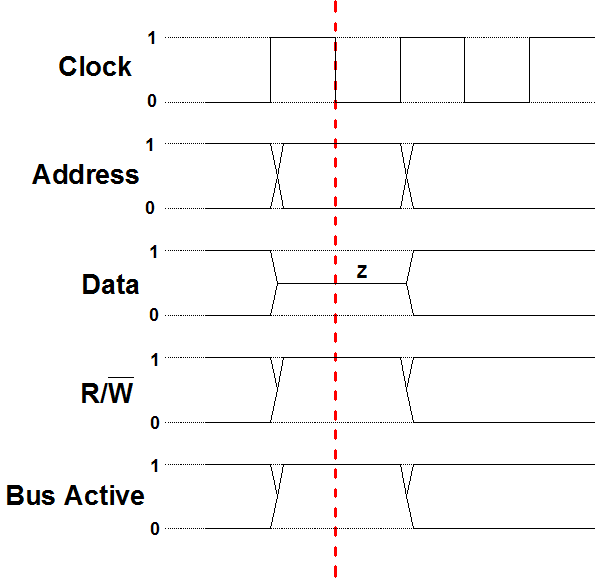

Dış Dünyadan Okuma

İşlemcinin dış dünyadan okuma işlemi yaparkenki sinyal durumları aşağıda gösterilmiştir.

"LDR" komutunun yürütülmesinde, clock'un yükselen kenarı ile Address istenen değere çekilirken R/W ve Bus_Active '1' konumuna gelir. Data sinyalleri ise verinin alınabilmesi için yüksek empedans(Z) konumuna geçer. Clock'un düşen kenarı(kırmızı çizgi ile belirtilen zaman) ile kaynaktan(belirtilen adresteki cihaz) örnekleme alınır ve komutta adı geçen registere veri aktarılır.

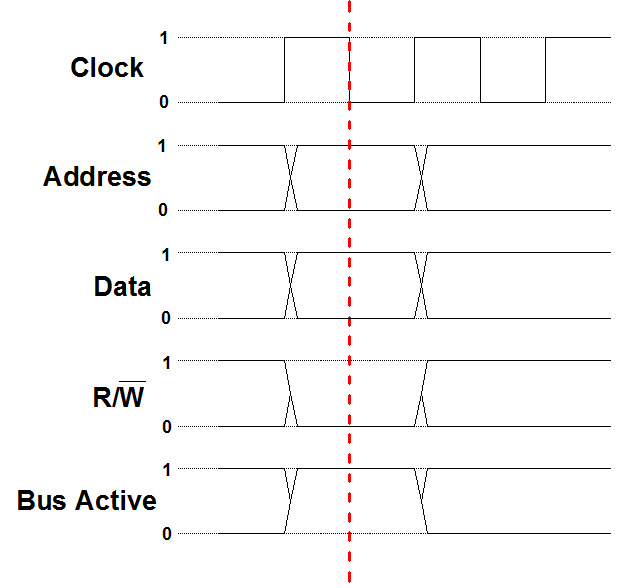

Dış Dünyaya Yazma

İşlemcinin dış dünyaya yazma işlemi yaparkenki sinyal durumları aşağıda gösterilmiştir.

"STR" komutunun yürütülmesinde yine clock'un yükselen kenarı ile Address ve Data istenilen değerlere ayarlanır. Bus_Active veri alışverişi yapılacağından dolayı '1' konumuna çekilir. Yazma işlemi yapılacağından R/W sinyali '0' konumuna çekilir.